By:-Gourav Kottawar

# Contents

| 3.1 Half / Full Adder                                              |

|--------------------------------------------------------------------|

| 3.2 Decoder / Encoder                                              |

| 3.3 Multiplexer / Demultiplexer,                                   |

| 3.4 Flip Flops - SR, D, JK, Master – Slave, Edge                   |

| Triggered                                                          |

|                                                                    |

| D flipflop with timing diagram                                     |

| D flipflop with timing diagram  3.5 Shift Registers (Any one type) |

|                                                                    |

| 3.5 Shift Registers (Any one type)                                 |

## Introduction

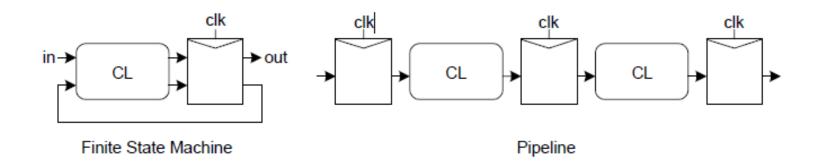

- There are two types of logic circuits

- Combinational Circuits

- Formed by combination of different logic circuits

- Outputs depend on the current inputs

- Ex- Multiplexer, De multiplexer, Encoder, Decoder

- No memory allocation required

- Sequential Circuits

- Outputs depend on current and previous inputs

- Requires separating previous, current and future

- Called states or tokens

- Example: Finite State Machines (FSMs), Pipelines

3/11/2016 By:-Gourav Kottawar

# Difference between Combinational and sequential circuits

| Combinational                                                                     | Sequential                                                                                                           |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Output of any instance of time depends only upon the input variables              | Output is generated dependent upon the present input variables and also on the basis of past history of these inputs |

| Memory unit is not required. i.e. it doesn't allocate any memory to the elements. | Memory unit is required i.e. it allocates any memory to the elements.                                                |

| Faster                                                                            | Slower                                                                                                               |

| Easy to design                                                                    | Difficult                                                                                                            |

| Parallel adder                                                                    | Serial adder                                                                                                         |

| Ex- Half and full adder Half and full subtractor MUX, DEMUX                       | Ex- Flip flops Shift registers Binary counters                                                                       |

## Adders

Computers implement arithmetic computations such as addition, subtraction, multiplication, division and many such operations using the concept of combinational circuits.

| <ul><li>Ex-</li></ul> | 1 | 1 | 0 |  |

|-----------------------|---|---|---|--|

|                       | 0 | 1 | 1 |  |

| 1                     | 0 | 0 | 1 |  |

- When addition of two k bits is computed the answer must be of k bits.

- But If the numbers are unsigned binary, the result can be K+1 bits.

- This k+1 bit is carry.

- Three types of Adder

- Half Addder Adder

- 2.Full Adder 3.Ripple carry

## 1. Half Adder

Half Adder: is a combinational circuit that performs the addition of two bits, this circuit needs two binary inputs and two binary outputs.

| Inputs      |   | Outputs |   |  |

|-------------|---|---------|---|--|

| X           | Y | С       | S |  |

| 0           | 0 | 0       | 0 |  |

| 0           | 1 | 0       | 1 |  |

| 1           | 0 | 0       | I |  |

| 1           | 1 | 1       | 0 |  |

| Truth table |   |         |   |  |

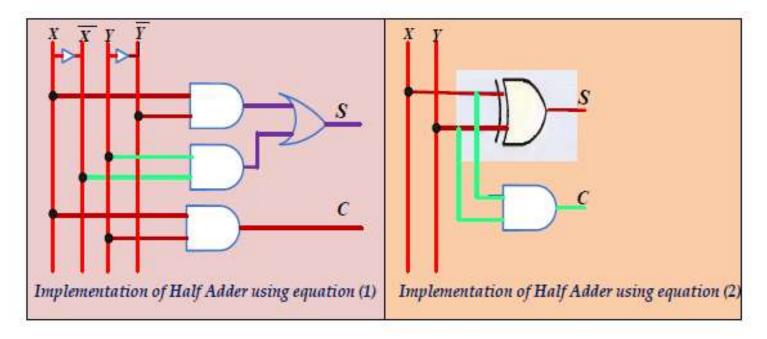

The simplified Boolean function from the truth table:

$$\begin{cases}

\mathbf{S} = \overline{\mathbf{X}}\mathbf{Y} + \mathbf{X}\overline{\mathbf{Y}} \\

\mathbf{C} = \mathbf{X}\mathbf{Y}

\end{cases}$$

(Using sum of product form)

Where S is the sum and C is the carry.

$${S = X \oplus Y \\ C = XY}$$

(Using XOR and AND Gates)

## 1. Half Adder

- The implementation of half adder using exclusive—OR and an AND gates is used to show that two half adders can be used to construct a full adder.

- The inputs to the XOR gate are also the inputs to the AND gate.

- Draw backs

- 1. Doesn't handle carries

- 2. Doesnot do further processing on carries.

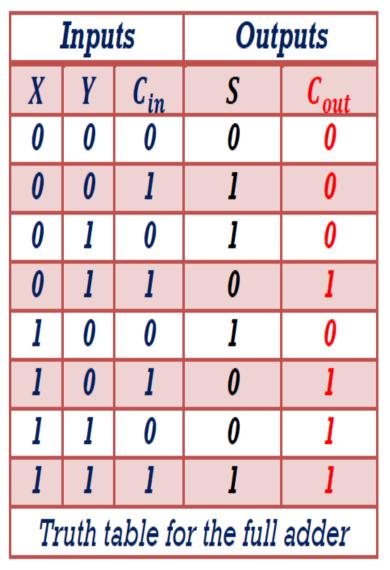

### 2. Full Adder

- Full Adder is a combinational circuit that performs the addition of three bits (two significant bits and previous carry).

- It consists of three inputs and two outputs, two inputs are the bits to be added, the third input represents the carry form the previous position.

- The full adder is usually a component in a cascade of adders, which add 8, 16 etc binary numbers.

- The **S** output is equal to **1** when only one input is equal to **1** or when all three inputs are equal to **1**.

- The  $C_{out}$  output has a carry 1 if two or three inputs are equal to 1.

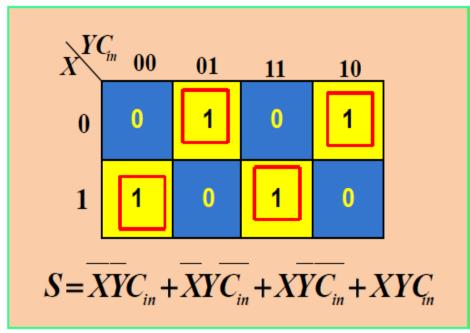

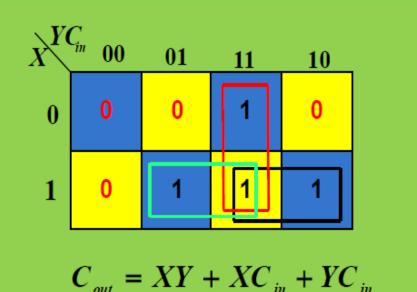

- The Karnaugh maps and the simplified expression are shown in the following figures:

$$\begin{cases} S = \overline{X} \, \overline{Y} C_{in} + \overline{X} Y \overline{C_{in}} + X \overline{Y} \, \overline{C_{in}} + X Y C_{in} \\ C_{out} = XY + X C_{in} + Y C_{in} \end{cases}$$

$$1 \begin{cases} Sum \ of \ products \end{cases}$$

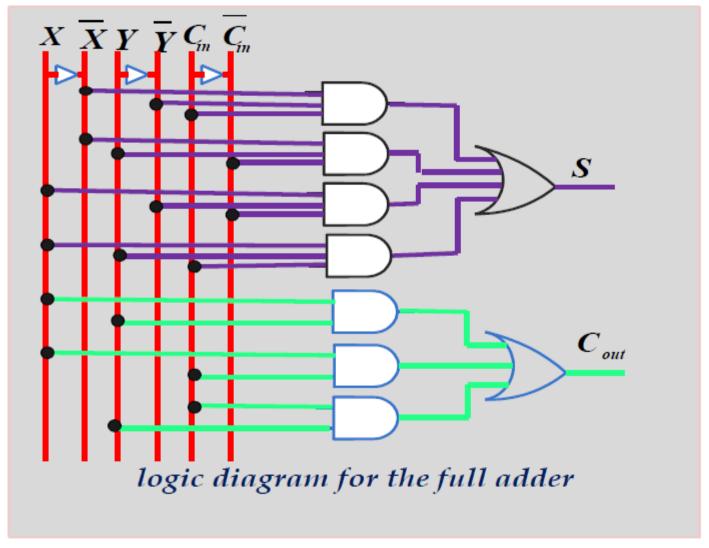

The *logic diagrams* for the full adder implemented in *sum-of-products* form are the following:

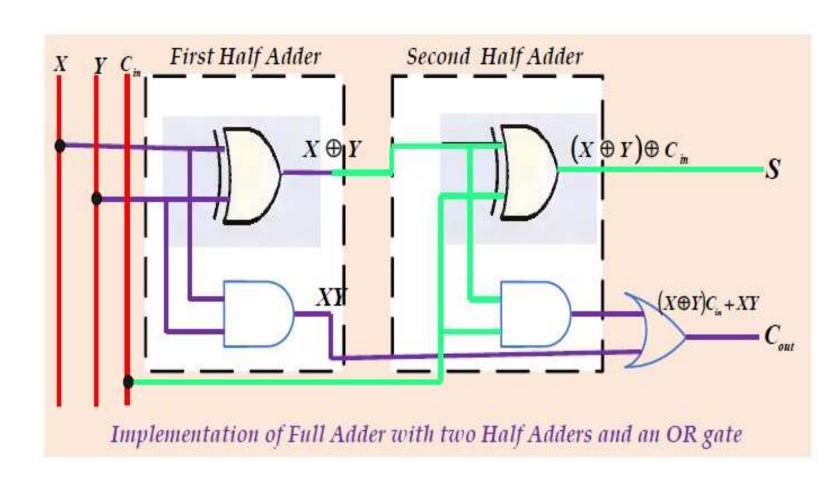

➤ It can also be implemented using two half adders and one OR gate (using XOR gates).

$$\begin{cases}

S = C_{in} \oplus (X \oplus Y) \\

C_{out} = C_{in} \cdot (X \oplus Y) + XY

\end{cases}$$

#### **Proof:**

#### The sum:

$$S = \overline{X} \, \overline{Y} C_{in} + \overline{X} Y \overline{C_{in}} + X \overline{Y} \, \overline{C_{in}} + X Y C_{in}$$

$$= \overline{C_{in}} (\overline{X} Y + X \overline{Y}) + C_{in} (\overline{X} \, \overline{Y} + X Y)$$

$$= \overline{C_{in}} (\overline{X} Y + X \overline{Y}) + C_{in} (\overline{X} Y + X \overline{Y})$$

$$S = C_{in} \oplus (X \oplus Y)$$

#### The carry output:

$$C_{out} = \overline{X}YC_{in} + X\overline{Y}C_{in} + XYC_{in} + XY\overline{C_{in}}$$

$$= C_{in}(\overline{X}Y + X\overline{Y}) + XY(C_{in} + \overline{C_{in}})$$

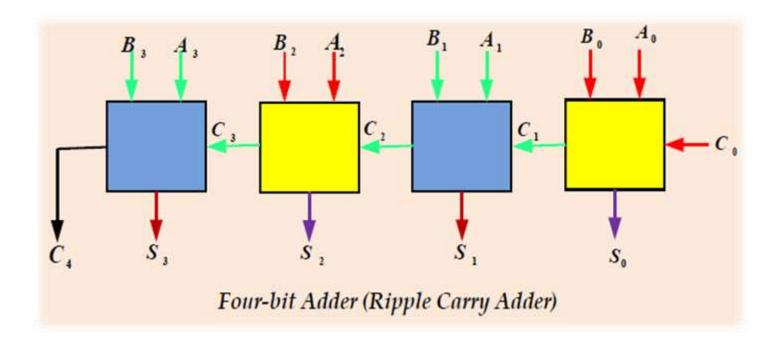

- A binary adder is a digital circuit that produces the arithmetic sum of two binary numbers.

- A binary adder can be constructed with full adders connected in cascade with the output carry form each full adder connected to the input carry of the next full adder in the chain.

- The four-bit adder is a typical example of a standard component. It can be used in many application involving arithmetic operations.

- The input carry to the adder is  $C_0$  and it ripples through the full adders to the output carry  $C_4$ .

- $\triangleright$  **n**-bit binary adder requires **n** full adders.

## Example

$$A + B$$

$$(A = 1011)$$

and  $(B = 0011)$

| Subscript i      | 3   | 2 | 1 | 0 |                    |           |

|------------------|-----|---|---|---|--------------------|-----------|

| Input Carry      | 0   | 1 | 1 | 0 | $C_i$              |           |

| $\boldsymbol{A}$ | . 1 | 0 | 1 | 1 | 4                  |           |

| +                | 1   | U | 1 | - | $A_i$              | $C_0 = 0$ |

| В                | 0   | 0 | 1 | 1 | $\boldsymbol{B_i}$ |           |

| Sum              | 1   | 1 | 1 | 0 | $S_i$              |           |

| Output Carry     | 0   | 0 | 1 | 1 | $C_{i+1}$          |           |

#### Carry Propagation

- The addition of A + B binary numbers in *parallel* implies that all the bits of A and B are available for computation at the same time.

- As in any combinational circuit, the signal must propagate through the gates before the correct output sum is available.

- ➤ The output will not be correct unless the signals are given enough time to propagate through the gates connected form the input to the output.

- ➤ The longest **propagation delay time** in an adder is the time it takes the carry to propagate through the full adders.

- The signal form the carry input  $C_i$  to the output carry  $C_{i+1}$  propagates through an **AND** gate and an **OR** gate, which equals **2** gate levels.

- o If there are 4 full adders in the binary adder, the output carry  $C_4$  would have  $2\times 4=8$  gate levels, form  $C_0$  to  $C_4$

- For an n-bit adder, 2n gate levels for the carry to propagate form input to output are required.

- > To reduce the carry propagation delay time:

- 1) Employ faster gates with reduced delays.

- Employ the principle of Carry Lookahead Logic.

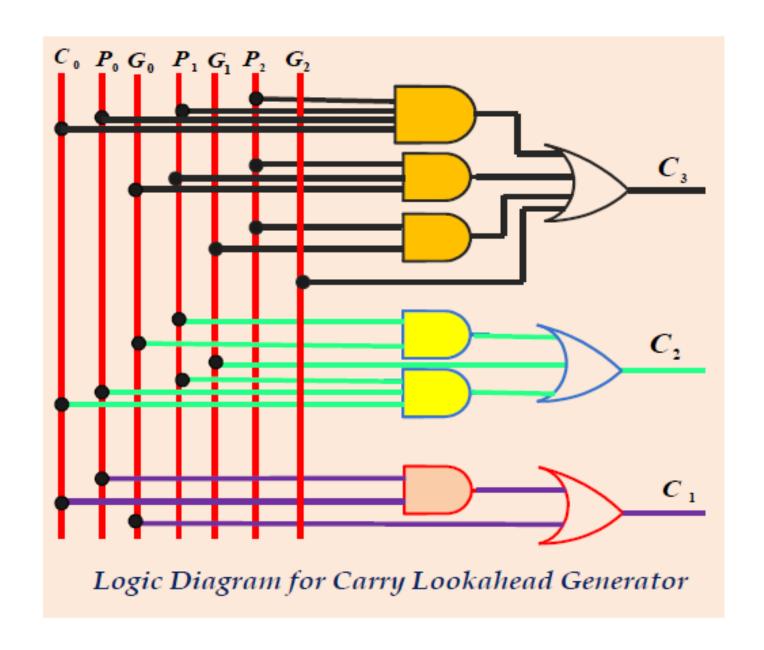

#### Proof: (using carry lookahead logic)

$$P_i = A_i \oplus B_i$$

$$G_i = A_i B_i$$

The output sum and carry are:

$$S_i = P_i \oplus C_i$$

$$C_{i+1} = G_i + P_i C_i$$

- ✓ G<sub>i</sub>-called a carry generate, and it produces a carry of I when both

A<sub>i</sub> and B<sub>i</sub> are I.

- $\checkmark$   $P_i$ -called a **carry propagate**, it determines whether a carry into stage i will propagate into stage i + 1.

- ✓ The *Boolean function* for the carry outputs of each stage and substitute the value of each C<sub>i</sub> form the previousoequationsuray Kottawar

$$\begin{cases} C_0 = input \ carry \\ C_1 = G_0 + P_0C_0 \\ C_2 = G_1 + P_1C_1 = G_1 + P_1(G_0 + P_0C_0) \\ = G_1 + P_1G_0 + P_1P_0C_0 \\ C_3 = G_2 + P_2C_2 = G_2 + P_2(G_1 + P_1G_0 + P_1P_0C_0) \\ = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_0 \end{cases}$$

$\triangleright$  The three Boolean functions  $C_1$ ,  $C_2$  and  $C_3$  are implemented in the *carry lookahead generator*.

The two level-circuit for the output carry  $C_4$  is not shown, it can be easily derived by the equation.

$\triangleright$   $C_3$  does not have to wait for  $C_2$  and  $C_1$  to propagate, in fact  $C_3$  is propagated at the same time as  $C_1$  and  $C_2$ .